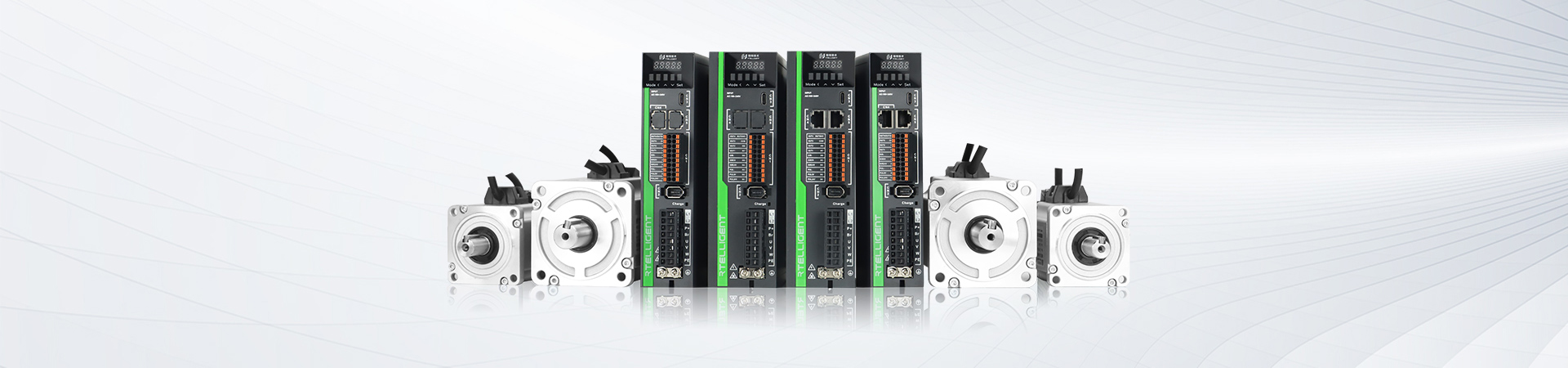

पाँचौं पुस्ताको उच्च-प्रदर्शन एसी सर्वो ड्राइभ पल्स R5 शृङ्खला R5L028M

प्रमुख विशेषताहरू

उच्च प्रदर्शन:

ARM + FPGA डुअल-चिप आर्किटेक्चर, ३kHz स्पीड लूप ब्यान्डविथ, २५०µs सिंक्रोनस साइकल, बहु-अक्ष समन्वयित प्रतिक्रिया छिटो र सटीक, ढिलाइ बिना सहज सञ्चालन सुनिश्चित गर्दै।

प्रयोगकर्ता-अनुकूलन योग्य I/O इन्टरफेसहरू:४ DI इनपुट र ४ DI आउटपुटहरू

पल्स इनपुट र RS485 सञ्चार:उच्च-गति भिन्न इनपुट: ४ मेगाहर्ट्ज सम्म, कम-गति इनपुट: २०० किलोहर्ट्ज (२४V) वा ५०० किलोहर्ट्ज (५V)

बिल्ट-इन रिजेनेरेटिभ रेजिस्टरले सुसज्जित।

नियन्त्रण मोडहरू:स्थिति, गति, टर्क, र हाइब्रिड लूप नियन्त्रण।

सर्भो सुविधाहरू समावेश:कम्पन दमन, जडता पहिचान, १६ कन्फिगर योग्य PR मार्गहरू, र साधारण सर्वो ट्युनिङ

५० वाट देखि ३००० वाट सम्म मूल्याङ्कन गरिएका मोटरहरूसँग उपयुक्त।

२३-बिट चुम्बकीय/अप्टिकल एन्कोडरहरूले सुसज्जित मोटरहरू।

वैकल्पिक होल्डिङ ब्रेक

STO (सुरक्षित टर्क अफ) प्रकार्य उपलब्ध छ

उत्पादन परिचय

तार रेखाचित्र

निर्दिष्टीकरणहरू

विद्युतीय प्यारामिटरहरू

21-300x300.jpg)